Un language de description hardware basé sur Haskell permettant de simuler ses composants en Haskell pure. Permet aussi de générer le design synthétisable en VHDL.

Archives mensuelles : janvier 2015

Du futur de Chisel

Comme on le sait, les membres du Berkeley Architecture Research group continuent à travailler d’arrache-pied sur Chisel.

On peut trouver un tutorial et les applications futures de Chisel ici (pdf).

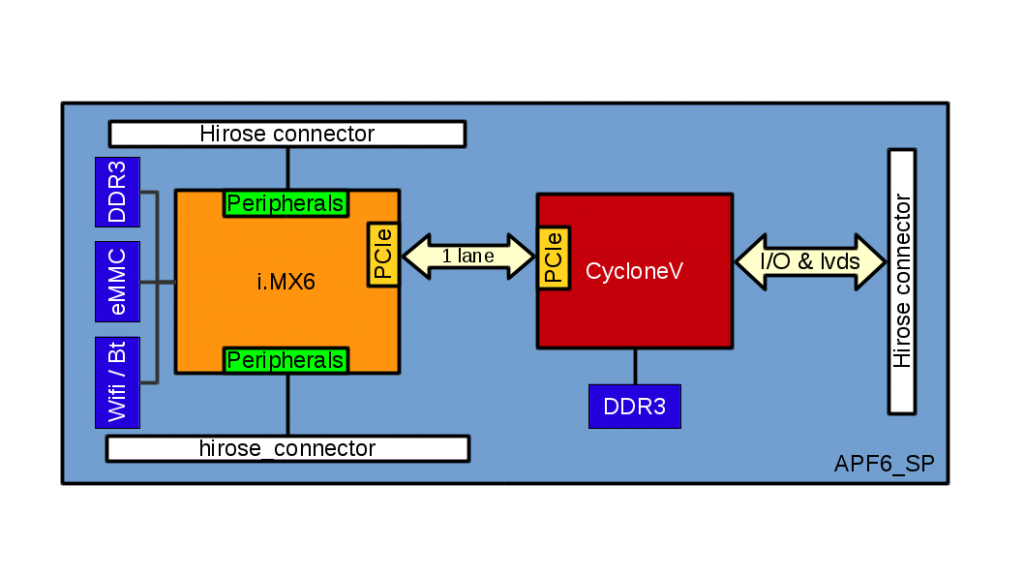

Un coprocesseur CycloneV via le PCIe avec l’APF6_SP

Armadeus systems sort une nouvelle carte à base de processeur + FPGA au mois de février 2015: l’APF6_SP.

Armadeus systems s’est spécialisée dans les modules proc + fpga. Ils avaient déjà l’APF27 à base d’i.MX27 et de spartan3a ainsi que l’AFP51 à base d’i.MX51 et de spartan6. Ces deux cartes possèdent un lien de type bus mémoire avec le processeur de manière à ce que le FPGA soit vu dans sont espace mémoire de la même manière que les autres périphériques.

L’APF6_SP est toujours à base de processeur i.MX de chez Freescale : l’i.MX6. Ce processeur se décline en version solo, dual ou quad core. Une des particularité de cette nouvelle carte est qu’elle utilise un FPGA de chez Altera plutôt que Xilinx.

Deux gros changement interviennent avec cette nouvelle carte :

- Le liens processeur-FPGA n’est plus de type «bus mémoire» mais utilise le PCI express. Ce qui le rend beaucoup plus standard.

- Deux puces de RAM DDR3 sont dédiées au FPGA, en plus de la RAM dédiée au processeur. Cette caractéristique ouvre des perspectives en matière de traitement d’images/vidéo; en effet il est possible de stocker des images entières dans la DDR; possibilitée qui est très limités en utilisant les blocks de ram interne au FPGA.

Mais pourquoi cette carte est-elle intéressante aux yeux du front de libération des FPGA ?

Car Armadeus Systems se base essentiellement sur des logiciels libres pour faire tourner ses modules. Le BSP est à base de buildroot, tous les outils de développement peuvent fonctionner sous Linux. Et pour le CycloneV, Quartus en version gratuite (web edition) sous Linux suffit.

Armadeus System joue la transparence avec une documentation abondante via un wiki et fournie tout son code sur sourceforge.

Enfin, un portage pour POD est en cours. Ce qui permettra d’utiliser un outils libre pour architecturer ses projets FPGA.

Un modulateur PWM en Chisel

Pour changer des LED qui clignotent, voici un modulateur PWM écrit en Chisel avec son testbench.

Le code ci-dessous (PWM.scala) est du Scala standard utilisant la librairie Chisel.

import Chisel._

/* Classe contenant le comportement du module */

class PWM extends Module {

/* Bundle io obligatoire */

val io = new Bundle {

val duty = UInt(INPUT, 8)

val out = Bool(OUTPUT)

}

/* Registre 8 bits pour le compteur */

val counter = Reg(UInt(width=8))

counter := counter + UInt(1)

/* Registre de sortie avec le comparateur */

io.out := Reg(next=(counter<io.duty))

}

/* Point d'entrée du programme */

object Example {

def main(args: Array[String]): Unit = {

chiselMain(args, () => Module(new PWM()))

}

}

Le code du modulateur ci-dessus est découpé en deux parties.

La première décrit le comportement du module. Elle comprend le bundle (similaire au record en VHDL) appelé io, qui doit être présent dans chacun des modules pour décrire les entrées et les sorties, un compteur 8 bits, et le registre de sortie qui est alimenté par le comparateur de rapport cyclique.

La deuxième partie est nécessaire pour le module qui se trouve au sommet de la hiérarchie afin de décrire le point d’entrée qui servira à la génération du code.

Il est aussi nécessaire de fournir le fichier build.sbt qui sert à indiquer a SBT (l’outil de build Scala) qu’il doit également aller chercher Chisel dans ses paquets avant de lancer la compilation. SBT va d’office compiler tout les fichiers Scala (avec l’extension .scala) qu’il trouve dans le répertoire courant.

libraryDependencies += "edu.berkeley.cs" %% "chisel" % "latest.release"

scalacOptions ++= Seq("-deprecation", "-feature", "-unchecked", "-language:reflectiveCalls")

Il faut ensuite s’assurer que Chisel génère du Verilog en lançant la commande

sbt 'run --v'

Il manque un banc de test pour exercer le design. Chisel propose de compiler également pour nous un modèle C++ du design qu’on peut obtenir

en utilisant la commande suivante :

sbt 'run --test --genHarness --vcd'

On va maintenant créer un testbench C++ qui permettra de générer les VCD. Appelons ce fichier main_pwm.cpp.

#include "PWM.h"

#include <iostream>

int main (int argc, char* argv[]) {

// Créer l'objet PWM

PWM_t* c = new PWM_t();

// Recupérer le nombre de cycles à exécuter

int lim = (argc > 1) ? atoi(argv[1]) : -1;

if(lim == -1) {

cout << "wrong argument, should be :" << endl;

cout << "a.out <n>" << endl;

return 1;

}

// Initialiser le modèle

c->init();

// Ecrire l'entête du VCD

c->dump_init(stdout);

// Ecrire le rapport cyclique

c->PWM__io_duty = LIT<8>(100);

for (int t = 0; lim < 0 || t < lim; t++) {

// Active le reset sur le premier cycle

dat_t<1> reset = LIT<1>(t == 0);

// Dump du VCD

c->dump(stdout,t);

// Avancer d'une période d'horloge

c->clock(reset);

}

}

Il reste juste à compiler le tout avec g++.

g++ PWM.cpp main_pwm.cpp

À exécuter

./a.out 10000 > out.vcd

Et admirer le résultat dans gtkwave

gtkwave out.vcd

Le FLF vous souhaite ses meilleurs vœux pour pour l’année 2015.

Que les outils pour les FPGA se libèrent et qu’ils se répandent dans tous les greniers et caves de tous les bidouilleurs.

Va-t-on voir émerger une chaîne de développement complète cette année ? Quelques signes donnent de l’espoir notamment du coté de VTR .

Bonne année 2015