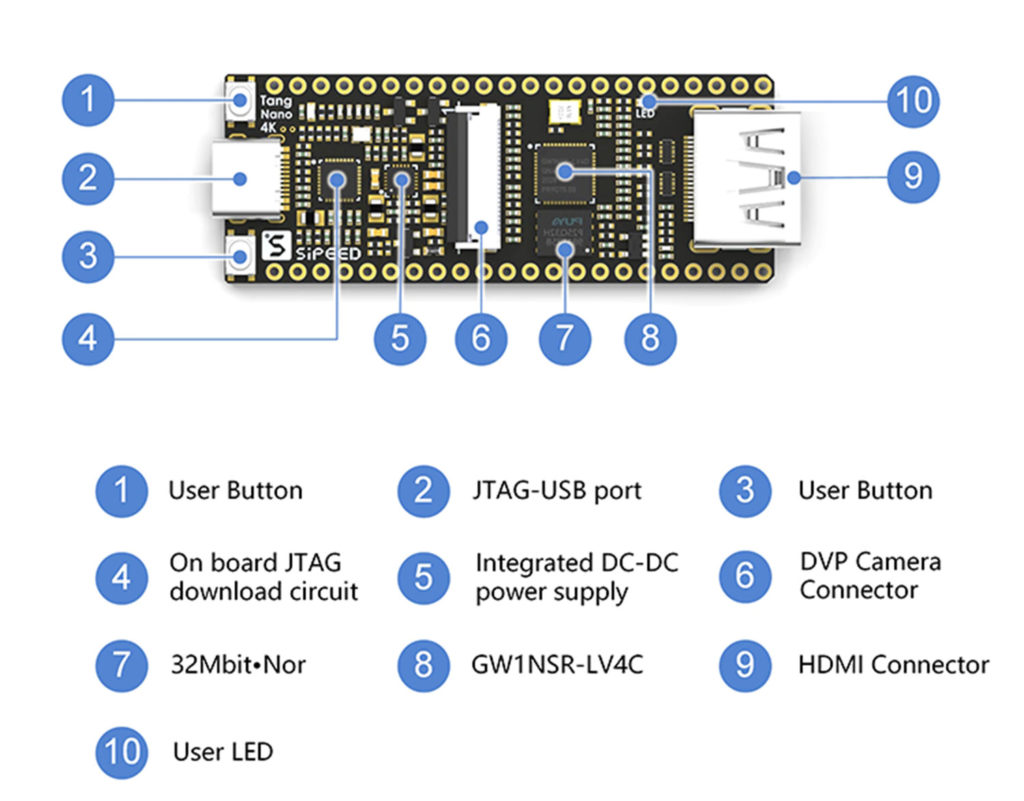

La désormais célèbre société chinoise Sipeed vient de sortir un tout petit kit de développement autour d’un FPGA Gowin et muni d’une sortie HDMI ainsi que d’une entrée caméra : la Tang Nano 4K.

Et non, elle n’est pas compatible avec des écrans HDMI 4K 😉 Le nom marketing bien choisi désigne le nombre de LUT disponibles.

Il est encore difficile de trouver des informations techniques sur cette carte, pourtant disponible (et rapidement livrée) sur aliexpress. Le wiki officiel est encore intégralement en chinois, mais on trouve le code d’exemple sur github. Le schéma de la carte est dispo sur le site de sipeed ici (ou sur le blog du flf si le firewall chinois fait des caprices 😉

À 18$ il n’était pas question de passer à coté, j’ai donc commandé une version avec caméra OV2640 ainsi qu’une version sans caméra :

Le tout pour une quarantaine d’€.

Branchement

Un câble USB-C est fourni dans la boite, voyons ce qu’il se passe au branchement de la version sans caméra:

sudo dmesg -c

[34644.177355] usb 1-2.1.1: new full-speed USB device number 14 using xhci_hcd

[34644.283502] usb 1-2.1.1: not running at top speed; connect to a high speed hub

[34644.305274] usb 1-2.1.1: New USB device found, idVendor=0403, idProduct=6010, bcdDevice= 5.00

[34644.305288] usb 1-2.1.1: New USB device strings: Mfr=1, Product=2, SerialNumber=3

[34644.305292] usb 1-2.1.1: Product: JTAG Debugger

[34644.305295] usb 1-2.1.1: Manufacturer: SIPEED

[34644.305298] usb 1-2.1.1: SerialNumber: FactoryAIOT Pro

[34644.311295] ftdi_sio 1-2.1.1:1.0: FTDI USB Serial Device converter detected

[34644.311336] usb 1-2.1.1: Detected FT2232C

[34644.316362] usb 1-2.1.1: FTDI USB Serial Device converter now attached to ttyUSB0

[34644.316513] ftdi_sio 1-2.1.1:1.1: FTDI USB Serial Device converter detected

[34644.316548] usb 1-2.1.1: Detected FT2232C

[34644.322352] usb 1-2.1.1: FTDI USB Serial Device converter now attached to ttyUSB1

La version avec caméra donne exactement la même chose.

Le dmesg de Linux laisse apparaître deux interfaces tty. L’une est certainement un convertisseur jtag pour configurer le FPGA et l’autre une interface uart permettant de communiquer avec l’application comme on a pu le voir avec la Tang Nano «classique».

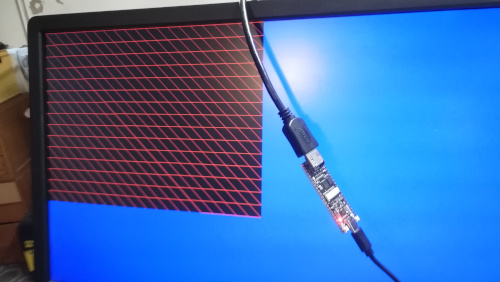

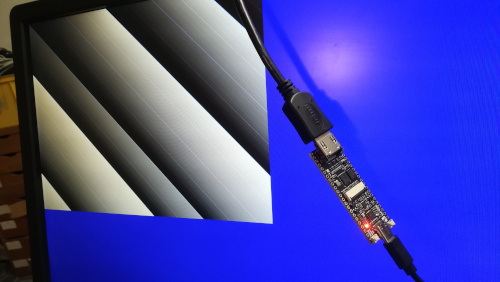

Si l’on branche un écran au HDMI on voit défiler quelques «pattern» avant de s’arrêter sur un écran vert sur fond bleu.

Pour le moment je n’ai pas réussi à obtenir grand chose de ces deux uarts.

Par la suite j’éditerais cet article pour vous parler de la configuration du FPGA.

Synthèse et configuration

Le plus simple pour commencer avec le kit est d’aller voir les deux projets proposés par Sipeed sur github et de les cloner.

$ git clone https://github.com/sipeed/TangNano-4K-example.git

$ cd TangNano-4K-example/Deux projets sont disponible dans ce dépôt, vus de loin l’un est pour faire clignoter une led et l’autre pour l’exemple HDMI programmé par défaut dans l’eeprom du kit :

$ ls

dk_video/ led_test/

Pour se faire la main il est donc naturel de commencer par la led.

Il faut d’abord lancer l’IDE officiel de gowin, comme décrit dans l’article de hackable-32 (le plus compliqué avec l’installation de gowin est d’obtenir la licence, après ça roule). Puis ouvrir le fichier de projet fourni nommé project/led_test.gprj et se trouvant dans le répertoire led_test/projet.

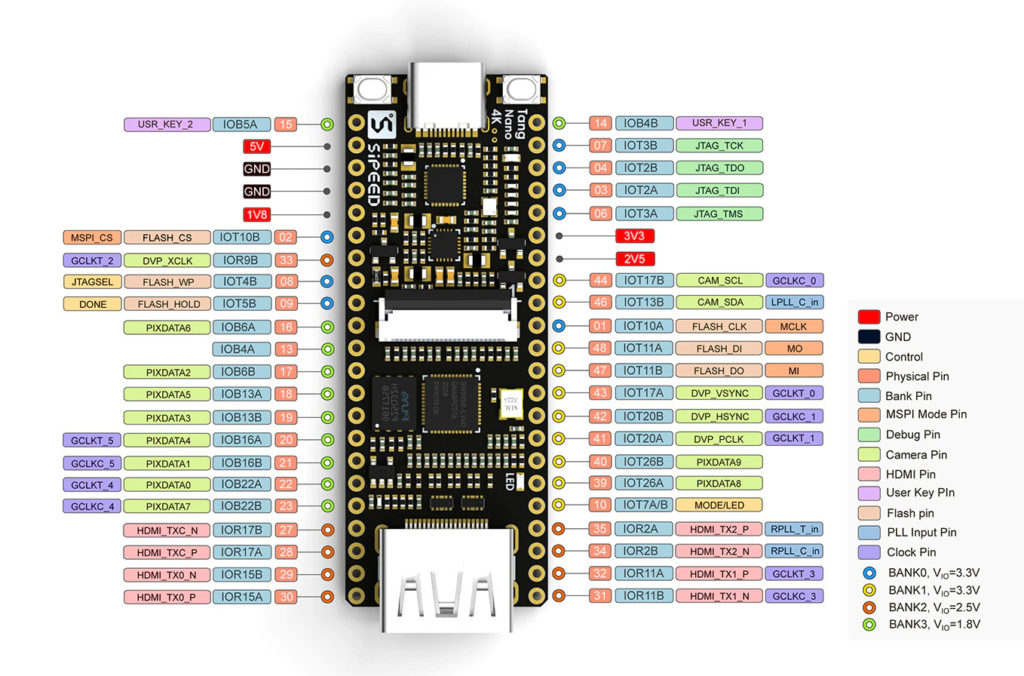

Le FPGA du kit se nomme GW1NSR-LV4CQN48PC7/I6 et le code Verilog de clignotement est le suivant. Quand au pinout le voici au format «cst» ci-dessous :

IO_LOC "led" 10;

IO_PORT "led" PULL_MODE=NONE DRIVE=8;

IO_LOC "sys_rst_n" 15;

IO_PORT "sys_rst_n" PULL_MODE=UP;

IO_LOC "sys_clk" 45;

IO_PORT "sys_clk" PULL_MODE=UP;Le projet est déjà synthétisé, si on souhaite le relancer il suffit de faire un clic-droit «rerun» sur «Synthesize» . Le bitstream est généré au format «fs» et se nomme project/impl/pnr/led_test.fs.

Le kit est désormais reconnu par openFPGALoader:

$ openFPGALoader --detect

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

index 0:

idcode 0x100981b

manufacturer Gowin

family GW1NSR

model GW1NSR-4C

irlength 8

Il suffit donc de programmer le bistrteam (format fs) au moyen de la commande :

$ openFPGALoader led_test/project/impl/pnr/led_test.fs

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse led_test/project/impl/pnr/led_test.fs:

Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

Flash SRAM: [==================================================] 100.00%

Done

SRAM Flash: Success

Et pour l’écrire dans l’eeprom il suffit d’ajouter l’option -f:

$ openFPGALoader ide/gbhdmi/impl/pnr/gbhdmi.fs -f

write to flash

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse ide/gbhdmi/impl/pnr/gbhdmi.fs:

Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

erase Flash Done

write Flash: [==================================================] 100.00%

Done

CRC check: Success

Le truc se programme et la led clignote.

Le HDMI

Le deuxième projet proposé dans le dépôt concerne le HDMI. Bon si on regarde le contenu du Top on se rend compte qu’il fait bien plus que le simple HDMI puisqu’il pilote également la ram, la Nor et la caméra.

Le générateur de pattern se charge également de générer les signaux de synchronisation vidéo. Mais ce qui nous intéresse particulièrement c’est le bloc qui pilote le HDMI. Ce bloc se prénomme DVI_TX_top et … il est encrypté 🙁

Le bloc est tout de même instanciable au moyen d’une BlackBox chisel. Ce qui permet d’adapter le projet GbVGA en GbHDMI

Pour la vidéo du montage en fonctionnement c’est par là.

La caméra OV2640

Je n’ai pas vu d’exemple de code utilisant la caméra ov2640 avec ce kit pour le moment. Il est probable que ça ne soit pas encore disponible.