[publié en premier sur Linuxfr]

Je pratique pas mal la conception sur ces drôles de bêtes que l’on appelle des FPGA. Les deux langages principaux pour décrire un composant FPGA sont le Verilog et le VHDL.

Pour développer son composant il est préférable de le simuler pour ensuite le synthétiser pour une cible et enfin le configurer et le tester «sur table».

S’il est aujourd’hui courant de simuler ses composants avec des logiciels libres comme GHDL, Icarus, NVC ou Verilator. Il est déjà plus compliqué de trouver des cibles compatibles avec les rares logiciels libre de synthèse comme Yosys ou abc.

Et ne parlons même pas des logiciels libre de placement routages comme nextpnr, vpr ou arachne-pnr (abandonné).

Mais une fois que l’on a trouvé une chaîne complètement libre pour son développement, il n’en reste pas moins qu’il faudra quand même acquérir une carte de développement pour faire ses tests réels.

On n’est pas à l’age du Claude ici, on fait pas ça sur un serveur installé on ne sais où et qui pompe toute l’eau et l’électricité des villes d’à coté…

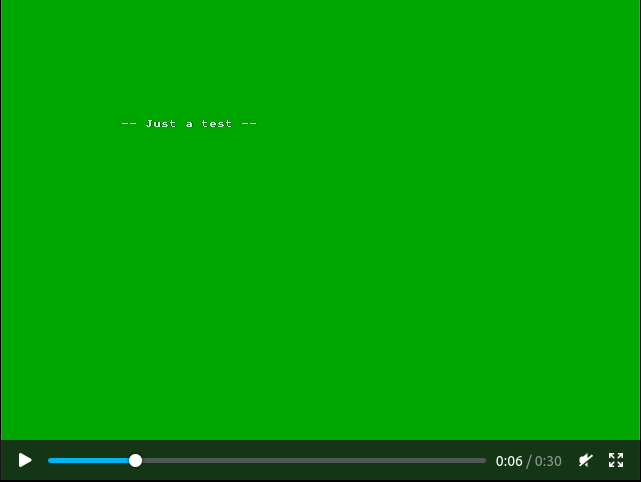

Et bien si ! JCM sur le net (un allemand ? bon le nom de domaine est à la Réunion, allez savoir …) s’est amusé à brancher une carte de développement Icepi Zero sur un ordinateur avec sa sortie vidéo (HDMI). Sur cet ordinateur tourne un service de synthèse/placementroutage/configuration/exécution du composant en VHDL/Verilog/Amaranth que vous lui envoyez et enregistre 30 secondes d’exécution de la vidéo qui sort sur le HDMI.

Il suffit pour cela de lui demander gentiment par message mastodon privé. Il synthétisera le design, postera la vidéo et les résultats de synthèse/P&R (nombre de cellules utilisés, vitesse max de l’horloge, …) sur son compte mastodon.

Le problème c’est que les instances mastodon limitent la taille des pouets. Alors il est bien sûr possible de copier coller chaque partie du code (par blocs de 666 caractères dans le cas de piaille.fr) mais c’est fastidieux et sujet à par mal d’erreur.

C’est pourquoi, mon cher journal, je te propose un petit script python qui se sert du fantastique client en console toot pour envoyer directement le fichier hdl que tu donneras en paramètre. Tu n’auras plus qu’à attendre quelques minutes pour voir apparaître la vidéo en gif sur ta timeline mastodon.

Le script se nomme masto_synth.py et se contente du nom du fichier à envoyer comme paramètre obligatoire.

$ python masto_synth.py -h

usage: masto_synth [-h] [-M MAX_CHAR] filename

Send an HDL file to @icepi-zero-bot@wafrn.jcm.re via mastodon

positional arguments:

filename HDL filename

options:

-h, --help show this help message and exit

-M MAX_CHAR, --max_char MAX_CHAR

Mastodon toot maximum chars size

need toot for mastodon postingBien sur on peut adapter la taille des pouets à son instance mastodon, ici c’est configuré à 500 par défaut.

Il faut avoir configuré toot au préalable pour être loggé :

$ toot loginUn fichier d’exemple est donné dans le profil de jcm que l’on peu modifier à sa guise (voir le fichier pif.vhd dans le dépôt du client).

L’envoi se fait simplement en ajoutant le chemin du fichier en unique paramètre :

$ python masto_synth.py pif.vhdOn attend quelques minutes (~3 minutes pour cet exemple) et …

On récupère les résultats avec la vidéo du fonctionnement de notre design.

La vidéo est totalement statique dans cet exemple, mais elle ouvre plein de perspectives de nuits blanches à jouer avec le kit sans même l’avoir acheté 🙂