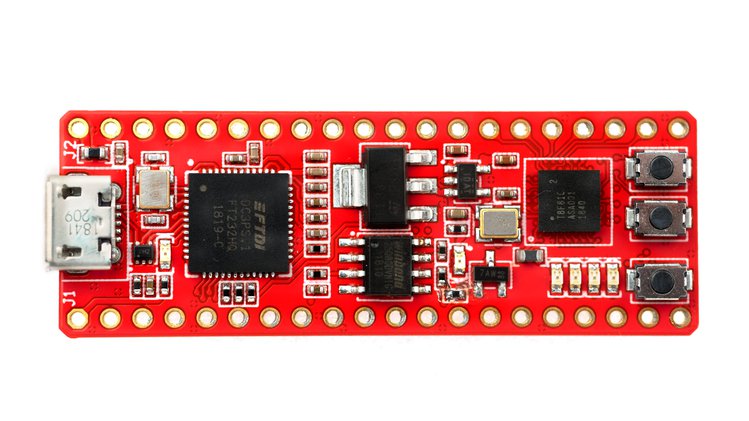

FireAnt est un kit de développement «de la taille d’un pouce» concu par la société Xips Technology et permettant de se faire la main sur le FPGA Trion T8 de la société Efinix.

Le kit est en crowdsourcing sur la plate-forme crowdsupply pour $30.

Pour ce prix on a le droit à :

- Un Trion T8F81C2 (dispo chez digikey) muni de

- 7384 Éléments logiques (LE)

- 123kb de RAM

- 8 multi-plieurs 18×18 bits

- Un FTDI pour piloter le kit en USB

- Une mémoire flash SPI à 104Mhz de 8Mo

- Et bien sûr un LDO pour l’alimentation 3v3 à partir de l’USB

Efinix est une toute nouvelle société qui propose des petits FPGA gravés en 40nm. Pour les tout petits FPGA de leur gamme, la société propose ce qu’elle appelle un MPM pour «Mask Programmable Memory» -> la possibilité de figer le design en usine et de ne plus avoir à configurer le FPGA à chaque démarrage.

Un IDE permettant de faire la synthèse, le placement-routage et le bitstream est fourni «gratuitement». À condition de posséder un kit de développement (J’ai beau négocier, ils ne veulent pas me le donner tant que je n’aurais pas reçu le kit 😉 ).

Bref, il n’est pas encore question d’outils libres pour ces FPGA pour l’instant. Cependant, ça fait du bien de voir de nouveaux acteurs dans le domaine des FPGA «physique».

Bonjour,

J’ai commandé un kit sur la plateforme Crowdsupply que j’ai reçu, et j’ai vu qu’il n’y a pas de serial number. Comment fait-on pour l’obtenir pour pouvoir accéder au logiciel de développement de Efinix sur leur site ?

Merci par avance.

Bonjour Marc,

À l’époque j’avais demandé directement au type de Jungle élec par mail fireant@xips.technology qui avait demandé à Efinix.

Leur système de licence qui expire n’est pas leur meilleur idée à mon avis.

Depuis j’ai utilisé le kit pour faire un adaptateur VGA pour gameboy si ça t’intéresse 😉

Merci Fabien pour ce retour.

J’ai finalement demandé directement en envoyant la photo de mon kit reçu au support europe de Efinix, et ils m’ont créé l’accès avec mon compte « Efinix ».

Pour la license je suis d’accord avec vous aussi…

J’ai eu une bizarrerie sous Efinix IDE (Windows), je n’arrive pas à ouvrir l’ « interface designer » pour définir mes IOs et PLL, j’ai eu cette erreur sous Console » sans jamais voir l’interface, et je ne sais pas pourquoi :

Interface design file does not exists, create and open design

Running Efinity Interface Designer…

Efinity Interface Designer finished. Exit code – 0 Exit status : Normal

Pourtant j’ai créé le projet avec « Create project », du coup, j’attends leurs réponses.

Oui, j’ai vu votre adaptateur VGA, c’est génial, en plus en Chisel 3.

Au fait votre site est vraiment super avec une mine d’information utile, bravo.

Ce problème me dit quelque chose, j’ai eu un truc similaire sous Linux je crois. Je vais essayer de regarder ça.

Merci 🙂

Bonjour,

J’attends toujours leur réponse, et je pense que j’ai pas de chance, car j’ai essayé aussi sous ubuntu, et tout ce passe bien jusqu’à :

rasp@ubuntuMarco:/opt/efinity/2021.1$ source bin/efinity_sh.sh

-bash: /opt/efinity/2021.1/bin/efinity: cannot execute binary file: Exec format error

Décidément, le sort s’acharne :), si tu as une idée, je suis preneur aussi sur cette erreur…

Merci.

Bonjour,

Je pense avoir trouvé pour le dernier problème, comme je tourne sous Ubuntu ARM, je pense que la distribution Efinix est sous Ubuntu x86 et donc compilé sous celle-ci, dommage…

Concernant le premier problème que j’ai rencontré sous windows, je cherche encore.

Merci.

Ha oui en effet, les joies des soft non-libre qu’on ne peut pas recompiler sur sa machine.

Je crois que c’était en effet le problème que j’avais eu, mais c’était une histoire de 32bits/64bits pour ma part.

Pour windows je ne sais pas, jamais essayé.

Bonjour,

Quelle fréquence de travaille max pouvons-nous obtenir avec le Trion8 de cette carte ?

Environ 80MHz max avec l’optimisation TIMING 3 ?

Comment pouvons-nous définir ceci ?

J’ai essayé ce petit bout de programme avec Chisel3 sous VSCODE:

import chisel3._

import chisel3.util._

class Blink extends Module {

val io = IO(new Bundle {

val led = Output(Bool())

})

val MAX_COUNT = 100000000

val count = Counter(MAX_COUNT)

count.inc()

io.led := 0.U

when(count.value <= (MAX_COUNT/2).U){

io.led := 1.U

}

}

class Top extends RawModule {

val led = IO(Output(Bool()))

val clock = IO(Input(Clock()))

val pllRstn = IO(Output(Bool()))

withClockAndReset(clock, false.B) {

pllRstn := true.B

val blink = Module(new Blink)

led := blink.io.led

}

}

object Hello extends App {

println("****************************")

println("* Generate verilog sources *")

println("****************************")

(new chisel3.stage.ChiselStage).emitVerilog(new Top())

}

Et avec le Verilog généré, et un niveau d'optimisation de TIMING 3, j'obtiens:

Maximum possible analyzed clocks frequency

Clock Name Period (ns) Frequency (MHz) Edge

clock 12.437 80.405 (R-R)

Geomean max period: 12.437

Launch Clock Capture Clock Constraint (ns) Slack (ns) Edge

clock clock 1.000 -11.437 (R-R)

Merci par avance,

Marc

Je pense qu’il vaut mieux poser la question sur le forum d’efinix. Je n’ai jamais cherché à optimiser les performances d’horloge du Trion personnellement.