Contrairement aux apparences, le logiciel de visualisation de Schéma/routage de Mentor (Maintenant siemens) PAD peut fonctionner sous Linux sans (trop) de problème.

Mais pourtant, la seule archive à télécharger sur le site officiel est un exe ?! Tout le monde sait qu’un fichier exe est un binaire exécutable pour Windows voir même pour DOS !

De fait, sous Linux, il est possible d’exécuter des exe grâce au vénérable wine. Ce logiciel n’est pas un logiciel franchouillard combattant la loi Évin.

Non ! c’est un émulateur windows qui permet d’exécuter des logiciels windows sous Linux.

En règle générale ça ne fonctionnne pas … Car l’émulation est toujours imparfaite, mais dans le cas du viewer Mentor/PAD le résultat est plutôt honorable et permet de visualiser des schéma/routage qu’on vous envoit.

Pour créer des cartes électroniques et/ou en éditer on préférera bien sur Kicad qui lui est parfaitement compatible avec Linux en plus d’être un logiciel libre.

Comment ça marche ?

On suppose que vous avez wine installé sur votre machine et que vous avez téléchargé l’archive de PADviewer . Il vous suffira ensuite de taper wine suivi du nom de l’archive :

$ wine PADSViewerVX.2.15_mib.exe

The most recent version of MIP is already installed in: c:\mentorgraphics\instal

l

MIP related file c:\mentorgraphics\install\tmp\FABIENM-TUXEDO-_32\ddinst32.exe w

as extracted successfully

MIP related file c:\mentorgraphics\install\tmp\FABIENM-TUXEDO-_32\vlhostid.exe w

as extracted successfully

MIP related file c:\mentorgraphics\install\tmp\FABIENM-TUXEDO-_32\ssidddp.sys wa

s extracted successfully

...

openjdk version "11.0.13" 2021-10-19

OpenJDK Runtime Environment Temurin-11.0.13+8 (build 11.0.13+8)

OpenJDK 64-Bit Server VM Temurin-11.0.13+8 (build 11.0.13+8, mixed mode)

053c:err:richedit:ReadStyleSheet skipping optional destination

053c:err:richedit:ReadStyleSheet skipping optional destination

053c:err:richedit:ReadStyleSheet skipping optional destination

053c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

061c:err:richedit:ReadStyleSheet skipping optional destination

0744:err:winediag:SECUR32_initNTLMSP ntlm_auth was not found or is outdated. Make sure that ntlm_auth >= 3.0.25 is in your path. Usually, you can find it in the winbind package of your distribution.

0744:err:ole:CoDisconnectObject apartment not initialised

075c:err:ole:CoDisconnectObject apartment not initialised

075c:err:ole:CoDisconnectObject apartment not initialised

Error getting install status ...Cela va lancer l’installeur graphique qui va décompresser l’archive avec quelques erreurs plus ou moins compréhensible à la micro$oft.

Une fois l’installation terminée, même avec erreur le programme se retrouvera installé dans votre home ~/.wine/drive_c :

~/.wine/drive_c/SiemensEDA/PADSVX.2.15Viewer/SDD_HOME/Programs/powerpcbviewer.exe

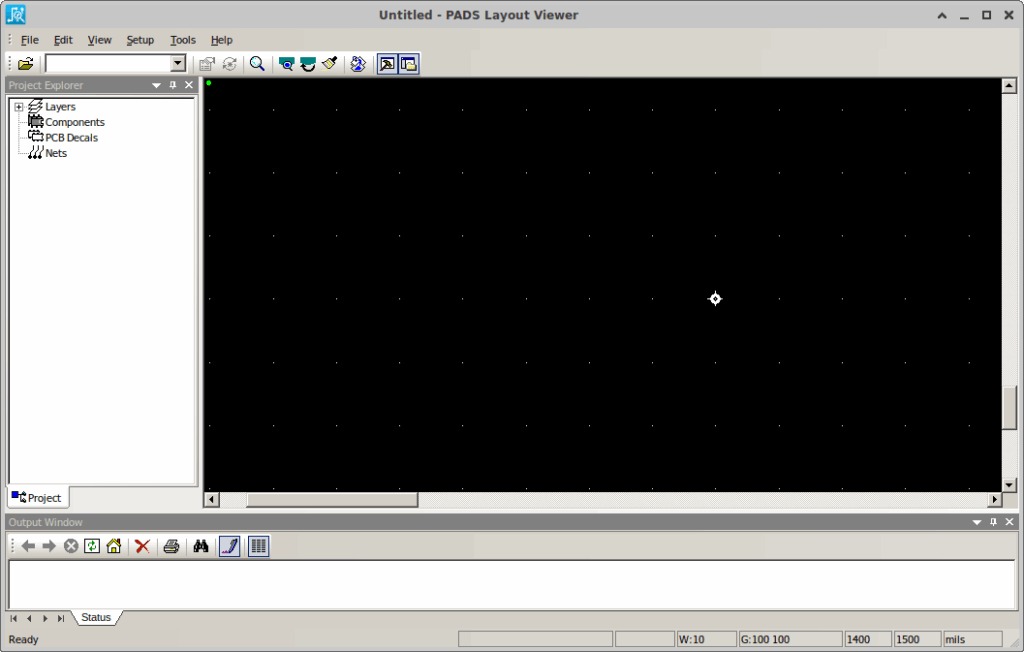

Programme que l’on pourra lancer, toujours avec wine pour visualiser son fichier pcb :

$ wine /home/user/.wine/drive_c/SiemensEDA/PADSVX.2.15Viewer/SDD_HOME/Programs/powerpcbviewer.exe

Pour le schéma (fichier sch) on utilisera powerlogicviewer.exe de la même manière.

Le viewer fonctionne assez bien, on arrive également à connecter le schéma avec le routage. Il y a quelques problèmes de police de caractères et parfois le logiciel plante, mais c’est un logiciel windows à l’origine, il y a des traditions à respecter 😉