Depuis quelques années, plusieurs nouveaux langages HDL basés sur des langages de programmations génériques émergent. Ces programmes peuvent être qualifiés de SSHDL pour Synchronous Synthesizable Hardware Description Language

HDL ?

Pour Hardware Description Langage, c’est un langage de description matériel. Un HDL permet de décrire le comportement d’un composant numérique, comme des bascule D, des ALU, ou des microprocesseurs complet.

Les deux HDL les plus connu sont bien sûr le VHDL et le Verilog. Se sont les seuls à être reconnu comme standard par tous les logiciels de synthèses du marché. C’est donc un passage obligé pour travailler sur les FPGA.

Synthesizable ?

Cela peut paraître étrange, mais VHDL/Verilog ont beau être supporté par tous les logiciels de synthèse du marché, se ne sont pas des langage que l’on peut considérer comme synthétisable. Seul un sous ensemble de ces deux langages l’est, le reste étant utilisé pour la simulation.

Une architecture décrite dans un langage synthétisable … sera synthétisable. Si une portion du code n’est pas synthétisable alors il y a une erreur de code.

Synchronous ?

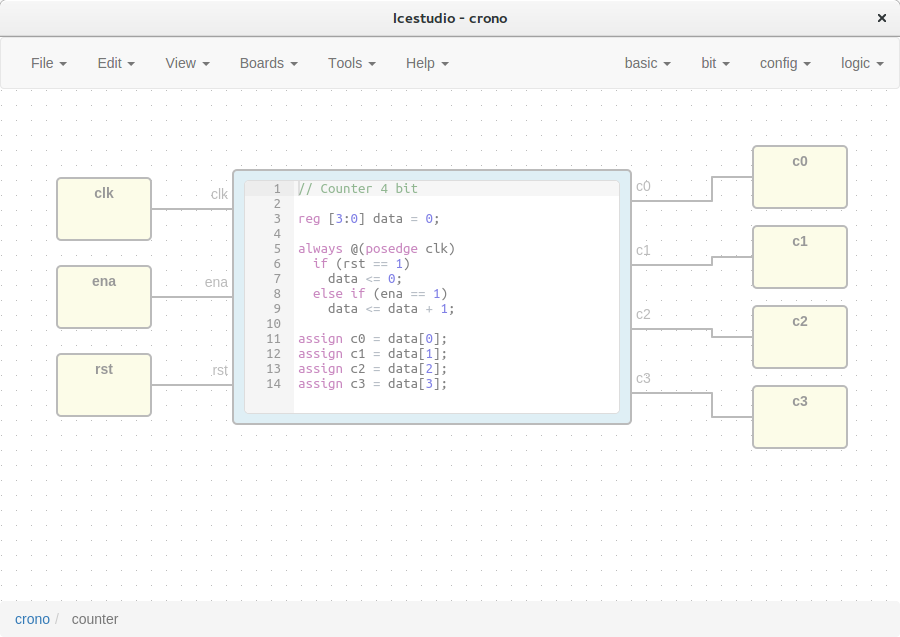

C’est quelque chose qui est indispensable en conception HDL. Tout le design doit être cadencé avec la même horloge, même si nous cherchons à capturer un événements extérieur (comme une interruptions) il est nécessaire de le resynchroniser avec l’horloge principale. Dans un SSHDL, le fonctionnement synchrone est implicite. L’horloge qui cadence tout le design n’a pas a être indiqué à chaque registre.

Toutes personnes qui a travaillé sur un FPGA de taille raisonnable le sait, il est impossible de cadencer tout son design avec la même horloge, puisque certain sous ensembles comme les contrôleurs de RAM ou les sérialiseur/déserialiseur nécessitent leurs propres horloges qui n’est généralement pas synchrone avec l’horloge globale. Il est alors nécessaire d’introduire la notion de domaines d’horloges et de soigner la conception des franchissement de domaines d’horloges de nos signaux (Clock domain crossing) afin d’éviter la métastabilité.

C’est un des points sensible qui fait la qualité d’un SSHDL : comment est géré le franchissement de domaines d’horloges ?

Standards industriels ou joujoux universitaires ?

Pour que ces langages puissent avoir un minimum d’espoir d’être déployés dans l’industrie, il faut que l’on puisse les utiliser sur les FPGA du marché. Il faut donc des logiciels capables de les synthétiser. Il est illusoire de croire que les gros fabricant de FPGA adoptent ces petits langages open-source pour leurs FPGA. Le SystemC est un bon exemple de langage qui n’a pas percé par manque de logiciel de synthèse (par contre il est très utilisé dans la simulation, car très rapide).

C’est pour cette raison que ces nouveaux langages ont choisi de générer leur designs en VHDL et/ou Verilog. Toutes la conception/simulation se fait donc avec ces nouveaux langages, et quand on veut faire la synthèse on lance la génération du VHDL/Verilog pour tester sur FPGA.

On peut ainsi considérer le VHDL/Verilog comme un langage «assembleur» du FPGA/ASIC.

Petites listes de SSHDL

La liste des SSHDL connus peut être trouvé dans la rubrique HDL de ce blog.