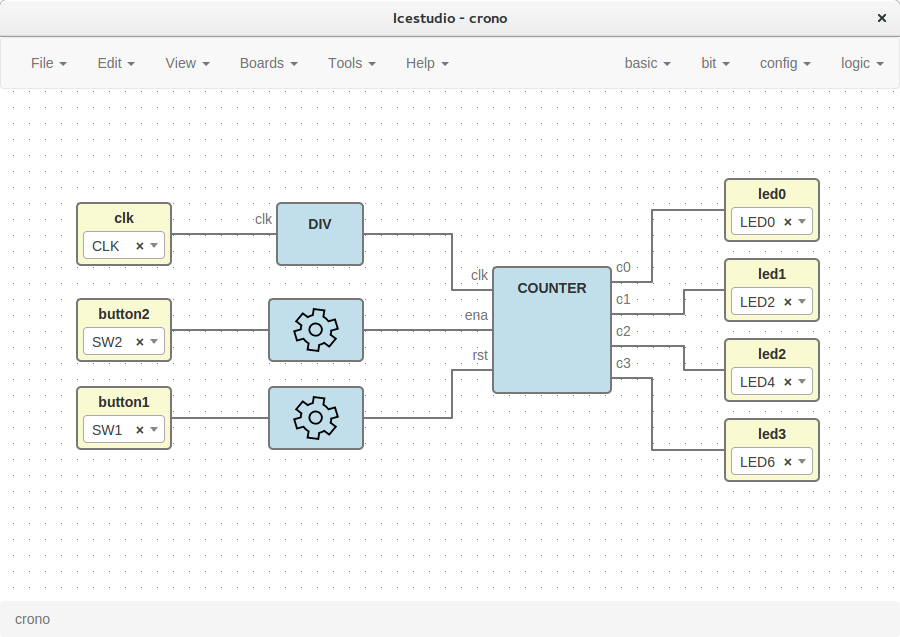

IceStudio est un logiciel graphique permettant de concevoir un design FPGA à la manière d’un schéma électronique.

Le logiciel est encore largement expérimentale (version 0.2) et centré sur les FPGA ice40 de chez lattice.

En fait, IceStudio se veut une extension graphique au projet IceStorm — chaine de synthèse/place&route/bitstream opensource —.

Architecturé en javascript autour de Nodejs, le logiciel permet de dessiner son projet au moyen de blocs reliés entre eux par des signaux.

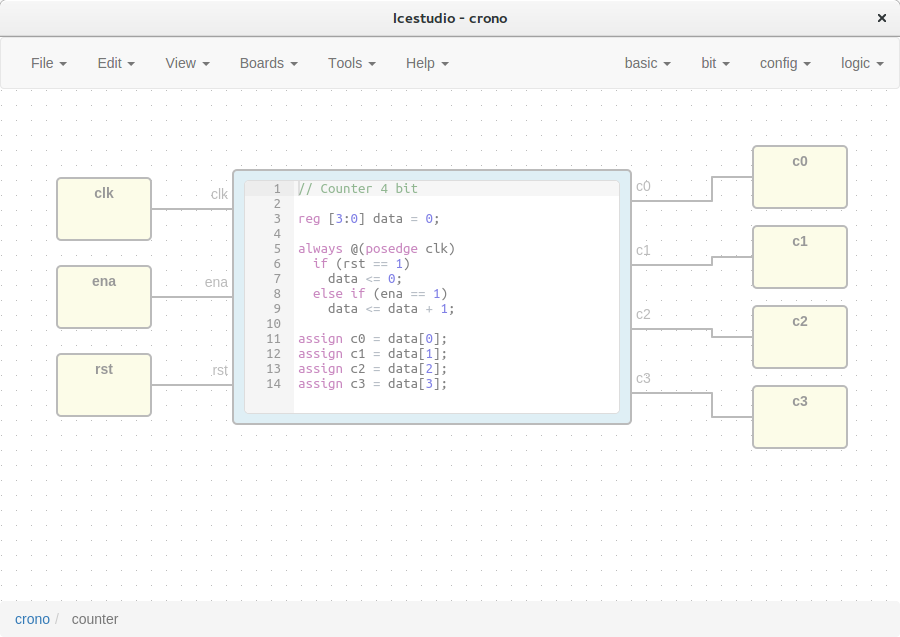

Les blocs peuvent être pris dans une librairie fourni avec le logiciel, mais il est également possible de créer des blocs «vierges» dans lesquels on écrira le code verilog correspondant au comportement souhaité.

Le format de sauvegarde du projet est en JSON, un outils de conversion permet ensuite de le transformer en code Verilog pour la synthèse.

Installation

Pour l’installer nous aurons besoin du paquet «npm» :

sudo apt-get install npmPuis de télécharger le projet git:

git clone https://github.com/FPGAwars/icestudio.gitEt enfin de lancer la commande d’installation comme décrite dans le README.md:

cd icestudio

npm installPour l’exécuter lancer simplement

npm startEt si comme pour votre serviteur, cela ne marche pas du tout 😉 allez plutôt chercher la release sur https://github.com/FPGAwars/icestudio/releases. Dézippez la

unzip Icestudio-0.2.0-beta2-linux64.zipPuis lancez le simplement :

./IcestudioLe projet est encore jeune mais très prometteur. Espérons que nous verrons rapidement l’intégration de nouvelles plateformes/FPGA, voir une version FPGA-Agnostic.