Armadeus systems sort une nouvelle carte à base de processeur + FPGA au mois de février 2015: l’APF6_SP.

Armadeus systems s’est spécialisée dans les modules proc + fpga. Ils avaient déjà l’APF27 à base d’i.MX27 et de spartan3a ainsi que l’AFP51 à base d’i.MX51 et de spartan6. Ces deux cartes possèdent un lien de type bus mémoire avec le processeur de manière à ce que le FPGA soit vu dans sont espace mémoire de la même manière que les autres périphériques.

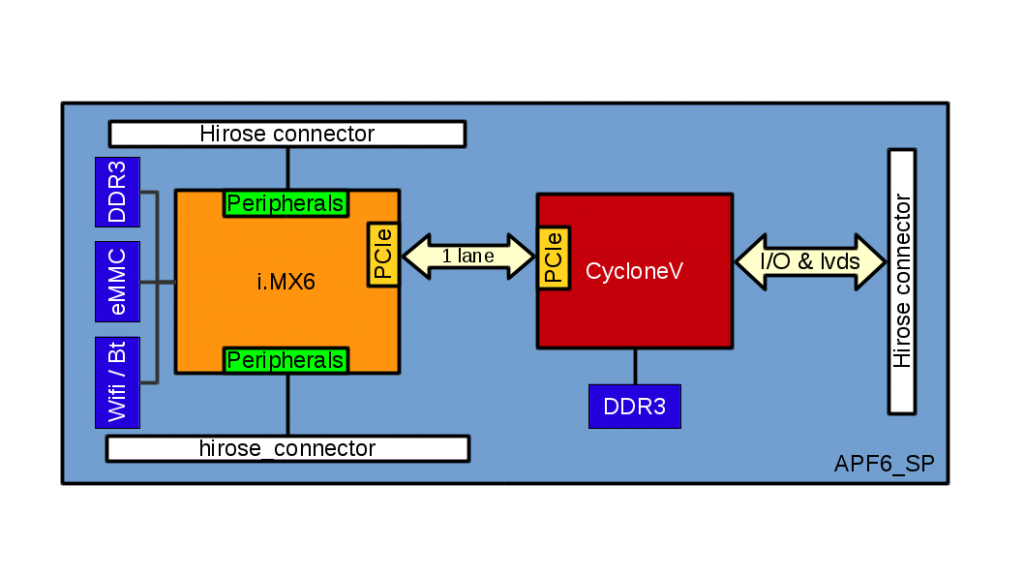

L’APF6_SP est toujours à base de processeur i.MX de chez Freescale : l’i.MX6. Ce processeur se décline en version solo, dual ou quad core. Une des particularité de cette nouvelle carte est qu’elle utilise un FPGA de chez Altera plutôt que Xilinx.

Deux gros changement interviennent avec cette nouvelle carte :

- Le liens processeur-FPGA n’est plus de type «bus mémoire» mais utilise le PCI express. Ce qui le rend beaucoup plus standard.

- Deux puces de RAM DDR3 sont dédiées au FPGA, en plus de la RAM dédiée au processeur. Cette caractéristique ouvre des perspectives en matière de traitement d’images/vidéo; en effet il est possible de stocker des images entières dans la DDR; possibilitée qui est très limités en utilisant les blocks de ram interne au FPGA.

Mais pourquoi cette carte est-elle intéressante aux yeux du front de libération des FPGA ?

Car Armadeus Systems se base essentiellement sur des logiciels libres pour faire tourner ses modules. Le BSP est à base de buildroot, tous les outils de développement peuvent fonctionner sous Linux. Et pour le CycloneV, Quartus en version gratuite (web edition) sous Linux suffit.

Armadeus System joue la transparence avec une documentation abondante via un wiki et fournie tout son code sur sourceforge.

Enfin, un portage pour POD est en cours. Ce qui permettra d’utiliser un outils libre pour architecturer ses projets FPGA.