Les chercheurs de Berkley qui ont fondé le set d’instruction (ISA) Risc-V (prononcez Risque failleve) ont également monté une société nommée SiFive.

Cette société conçoit des cœurs de processeurs nommés Freedom Everywhere et propose à ses clients de l’inclure dans des ASIC personnalisé. Les processeurs créés restent évidemment open-source, et l’intégralité du code (Chisel) est disponible sur le site de SiFive.

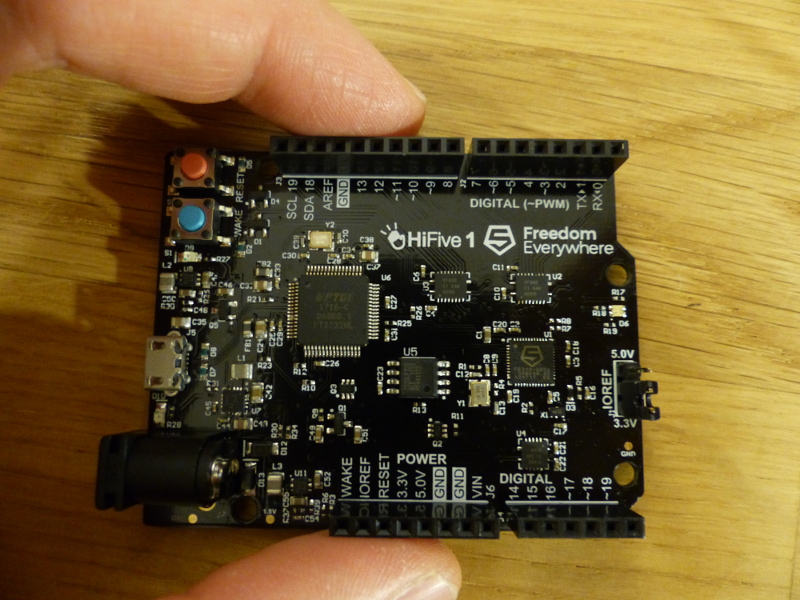

Pour promouvoir leur processeur, SiFive a fabriqué un microcontrôleur 32bits nommé Freedom E310. SiFive a également réalisé une carte «compatible arduino» qu’il est possible de commander en crowdsourcing pour prendre en main ce processeur.

C’est ce que nous allons tester ici. Le kit est livré «sec», pour l’alimenter il faut donc soit trouver un câble d’alimentation, soit décider de l’alimenter via l’USB comme expliqué dans le manuel de démarrage.

Le plus gros composant que l’on voit sur la carte est le convertisseur USB-Série et non le microcontrôleur. Le microcontrôleur se trouve à droite avec le «symbole superman».

Branchement

Le branchement du kit sur l’USB fait apparaître deux convertisseurs FTDI :

[16353.800810] usb 3-1: new high-speed USB device number 2 using xhci_hcd [16353.941120] usb 3-1: New USB device found, idVendor=0403, idProduct=6010 [16353.941124] usb 3-1: New USB device strings: Mfr=1, Product=2, SerialNumber=0 [16353.941126] usb 3-1: Product: Dual RS232-HS [16353.941139] usb 3-1: Manufacturer: FTDI [16354.969029] usbcore: registered new interface driver usbserial [16354.969056] usbcore: registered new interface driver usbserial_generic [16354.969076] usbserial: USB Serial support registered for generic [16354.986140] usbcore: registered new interface driver ftdi_sio [16354.986162] usbserial: USB Serial support registered for FTDI USB Serial Device [16354.986298] ftdi_sio 3-1:1.0: FTDI USB Serial Device converter detected [16354.986354] usb 3-1: Detected FT2232H [16354.986609] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB0 [16354.986634] ftdi_sio 3-1:1.1: FTDI USB Serial Device converter detected [16354.986673] usb 3-1: Detected FT2232H [16354.986906] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB1

La carte est livrée avec un bootloader faisant clignoter la led 4-couleurs D6. Il est possible de communiquer avec ce programme via le second port série :

$ sudo screen /dev/ttyUSB1 115200

On obtient le message de superman après avoir appuyé sur reset:

SIFIVE, INC.

5555555555555555555555555

5555 5555

5555 5555

5555 5555

5555 5555555555555555555555

5555 555555555555555555555555

5555 5555

5555 5555

5555 5555

5555555555555555555555555555 55555

55555 555555555 55555

55555 55555 55555

55555 5 55555

55555 55555

55555 55555

55555 55555

55555 55555

55555 55555

555555555

55555

5

'led_fade' Demo

55555555555555555555555555555555555555555555555

5555555 Are the LEDs Changing? [y/n] 555555555

55555555555555555555555555555555555555555555555

y

PASS

Compilons un programme pour l’E310

La mise en route du kit est relativement simple dans la mesure ou tout est décrit dans le document «getting started».

Évidemment, le cœur du proc est libre, du coup la chaîne de compilation l’est aussi pardi. Il suffit de la télécharger sur sa machine :

$ git clone --recursive https://github.com/sifive/freedom-e-sdk.git

Puis

cd freedom-e-sdk make tools

Et attendre que ça compile en prenant son café.

Dans mon cas (Debian jessie) il fallait également installer les packets suivant pour que ça compile:

sudo apt-get install libmpc-dev

Un fois installé, on peut compiler la démo de gpio comme ça:

$ make software PROGRAM=demo_gpio BOARD=freedom-e300-hifive1

Puis la télécharger ainsi :

$ make upload PROGRAM=demo_gpio BOARD=freedom-e300-hifive1 work/build/openocd/prefix/bin/openocd -f bsp/env/freedom-e300-hifive1/openocd.cfg & \ /opt/freedom-e-sdk/work/build/riscv-gnu-toolchain/riscv64-unknown-elf/prefix/bin/riscv64-unknown-elf-gdb software/demo_gpio/demo_gpio --batch -ex "set remotetimeout 240" -ex "target extended-remote localhost:3333" -ex "monitor reset halt" -ex "monitor flash protect 0 64 last off" -ex "load" -ex "monitor resume" -ex "monitor shutdown" -ex "quit" && \ echo "Successfully uploaded 'demo_gpio' to freedom-e300-hifive1." Open On-Chip Debugger 0.10.0+dev (2017-11-18-18:04) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html adapter speed: 10000 kHz Info : auto-selecting first available session transport "jtag". To override use 'transport select '. Info : ftdi: if you experience problems at higher adapter clocks, try the command "ftdi_tdo_sample_edge falling" Info : clock speed 10000 kHz Info : JTAG tap: riscv.cpu tap/device found: 0x10e31913 (mfg: 0x489 (SiFive, Inc.), part: 0x0e31, ver: 0x1) Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=0 Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=1 Info : Examined RISCV core; XLEN=32, misa=0x40001105 Info : Listening on port 3333 for gdb connections Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=2 Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=3 Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=4 Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=5 Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=6 Info : dtmcontrol_idle=5, dbus_busy_delay=1, interrupt_high_delay=7 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=7 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=8 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=9 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=10 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=12 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=14 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=16 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=18 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=20 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=23 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=26 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=29 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=32 Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=36 Info : [0] Found 2 triggers halted at 0x204000fe due to debug interrupt Info : Listening on port 6666 for tcl connections Info : Listening on port 4444 for telnet connections Info : accepting 'gdb' connection on tcp/3333 Info : Found flash device 'issi is25lp128' (ID 0x0018609d) trap_entry () at /opt/freedom-e-sdk/bsp/env/entry.S:41 41 STORE x27, 27*REGBYTES(sp) Info : JTAG tap: riscv.cpu tap/device found: 0x10e31913 (mfg: 0x489 (SiFive, Inc.), part: 0x0e31, ver: 0x1) JTAG tap: riscv.cpu tap/device found: 0x10e31913 (mfg: 0x489 (SiFive, Inc.), part: 0x0e31, ver: 0x1) halted at 0x204000fe due to debug interrupt halted at 0x204000fe due to debug interrupt cleared protection for sectors 64 through 255 on flash bank 0 cleared protection for sectors 64 through 255 on flash bank 0 Info : JTAG tap: riscv.cpu tap/device found: 0x10e31913 (mfg: 0x489 (SiFive, Inc.), part: 0x0e31, ver: 0x1) halted at 0x204000fe due to debug interrupt Loading section .init, size 0x6c lma 0x20400000 Loading section .text, size 0xbbe6 lma 0x2040006c Loading section .rodata, size 0x1144 lma 0x2040bc58 Loading section .eh_frame, size 0x68 lma 0x2040cd9c Loading section .data, size 0x9d0 lma 0x2040ce04 Info : Padding image section 0 with 6 bytes Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=40 Info : Retrying memory read starting from 0x80000000 with more delays Info : dtmcontrol_idle=5, dbus_busy_delay=2, interrupt_high_delay=45 Info : Retrying memory read starting from 0x80000000 with more delays halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint halted at 0x80000004 due to software breakpoint Info : JTAG tap: riscv.cpu tap/device found: 0x10e31913 (mfg: 0x489 (SiFive, Inc.), part: 0x0e31, ver: 0x1) halted at 0x80000004 due to software breakpoint Start address 0x20400000, load size 55246 Transfer rate: 52 KB/sec, 6905 bytes/write. halted at 0x20400004 due to step halted at 0x20400004 due to step shutdown command invoked shutdown command invoked A debugging session is active. Inferior 1 [Remote target] will be detached. Quit anyway? (y or n) [answered Y; input not from terminal] Remote communication error. Target disconnected.: Connection reset by peer. Successfully uploaded 'demo_gpio' to freedom-e300-hifive1.

Malgrés l’erreur, visiblement le programme a bien été téléchargé dans le micro puisque les leds s’allument bien alternativement.

Et surtout, le message de démarrage s’affiche bien sur le /dev/ttyUSB1 :

core freq at 266646323 Hz

SIFIVE, INC.

5555555555555555555555555

5555 5555

5555 5555

5555 5555

5555 5555555555555555555555

5555 555555555555555555555555

5555 5555

5555 5555

5555 5555

5555555555555555555555555555 55555

55555 555555555 55555

55555 55555 55555

55555 5 55555

55555 55555

55555 55555

55555 55555

55555 55555

55555 55555

555555555

55555

5

SiFive E-Series Software Development Kit 'demo_gpio' program.

Every 2 second, the Timer Interrupt will invert the LEDs.

(Arty Dev Kit Only): Press Buttons 0, 1, 2 to Set the LEDs.

Pin 19 (HiFive1) or A5 (Arty Dev Kit) is being bit-banged

for GPIO speed demonstration.

.

Avec arduino

Ça n’est pas pour rien que le kit ressemble à s’y méprendre à un arduino : il est possible d’utiliser l’ide d’arduino pour se connecter à la carte.

L’ide arduino se trouvant dans ma debian est trop vieux pour pouvoir ajouter la toolchaine sifive. J’ai donc du télécharger la 1.8 puis l’installer. Heureusement ça n’est pas très compliqué :

$ tar -Jxvf arduino-1.8.5-linux64.tar.xz $ cd arduino-1.8.5/ $ ./install.sh $ ./arduino

Une fois lancé, il faut ajouter la configuration du package sifive en allant dans les préférences pour ajouter l’url suivante :

http://static.dev.sifive.com/bsp/arduino/package_sifive_index.json

Puis installer la plate-forme «sifive» via le board manager. Il faut également sélectionner «SiFive open ocd» comme programmeur.

Ne pas oublier de relancer l’ide et roulez jeunesse ! On peut facilement compiler/télécharger l’exemple de clignotement de led.