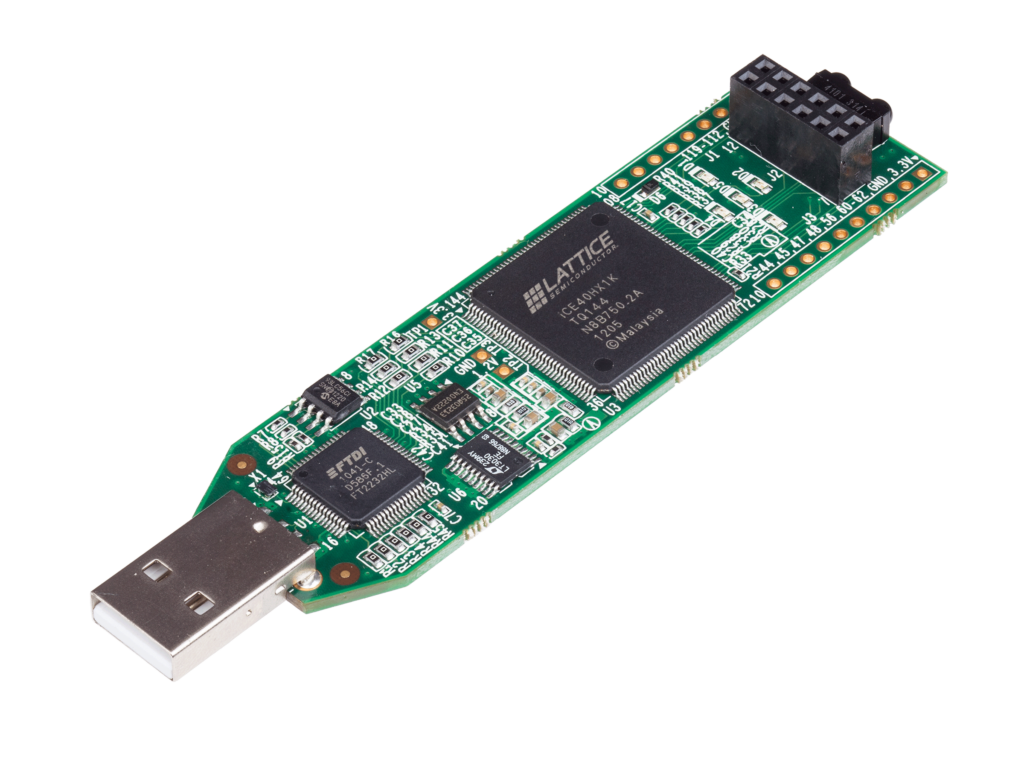

Historiquement le ICE40 soudé sur la carte icestick est le premier supporté par des outils libres.

Il est maintenant possible d’utiliser plusieurs programmes open-source pour développer dessus. Voici une méthode avec yosys, nextpnr, icestorm et openFPGALoader.

Dans un premier temps, allez donc cloner, compiler makeInstaller les 4 programmes cités ci-avant :

- Yosys: Logiciel de synthèse Verilog couteau suisse du monde du FPGA.

- nextpnr: Logiciel de placement routage supportant de plus en plus de famille de FPGA

- icestorm: La tempête à l’origine de la libération des ICE40 de Lattice.

- openFPGALoader: Le configurateur universel pour FPGA.

N’oubliez pas l’option de compilation «ICE40» quand elle est requise, mais c’est expliqué dans les différents tutos de compilation des outils.

Une fois que tout est installé on peut prendre le source Verilog «Blinking Led Project» et le modifier comme ci-dessous :

module blink (

// Horloge

input clock,

output led

);

// Icestick clock : 12Mhz

parameter clock_freq = 12_000_000; // clock frequency

localparam MAX_COUNT = clock_freq;

localparam MAX_COUNT_UPPER = $clog2(MAX_COUNT) - 1;

reg [MAX_COUNT_UPPER:0] counter;

reg led_reg;

assign led = led_reg;

always@(posedge clock)

begin

if(counter < MAX_COUNT/2)

led_reg <= 1;

else

led_reg <= 0;

if(counter >= MAX_COUNT)

counter <= 0;

else

counter <= counter + 1;

end

endmoduleIl faut ensuite ajouter les informations de pinout pour l’horloge et la LED dans un fichier pcf que nous nommerons blink.pcf:

set_io clock 21

set_io led 98Puis enfin, lancer les différentes commande de synthèse/pnr/bitstream :

$ PROJECTNAME=blink

$ VERILOGS="$PROJECTNAME.v"- Synthèse avec yosys:

$ yosys -q -p "synth_ice40 -top $PROJECTNAME -json $PROJECTNAME.json" $VERILOGS- Placement routage avec nextpnr:

$ nextpnr-ice40 --force --json $PROJECTNAME.json --pcf $PROJECTNAME.pcf --asc $PROJECTNAME.asc --freq 12 --hx1k --package tq144 $1

- Vérification des timings avec icetime:

$ icetime -p $PROJECTNAME.pcf -P tq144 -r $PROJECTNAME.timings -d hx1k -t $PROJECTNAME.asc

// Reading input .pcf file..

// Reading input .asc file..

// Reading 1k chipdb file..

// Creating timing netlist..

// Timing estimate: 6.12 ns (163.28 MHz)

- Packaging du bitstream avec icepack :

$ icepack $PROJECTNAME.asc $PROJECTNAME.bin

- Configuration du fpga avec openFPGALoader:

$ openFPGALoader -b ice40_generic blink.bin

write to ram

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file DONE

00

Detail:

Jedec ID : 20

memory type : ba

memory capacity : 16

EDID + CFD length : 10

EDID : 0000

CFD :

Erasing: [==================================================] 100.00%

Done

Writing: [==================================================] 100.00%

Done

Wait for CDONE DONE

Et voila, la LED clignote.