Le processus de synthèse/placement/routage/bitstream prenant beaucoup de temps, on est amené à faire d’autres activité pendant le traitement. Ce «switch» de tâche nous amène à faire des erreurs fréquentes de version de bitstream au moment de la configuration du FPGA.

Il est fréquent de passer des heures voir des jours sur un bug qui n’en était finalement pas un puisque nous n’avions pas mis à jour la version du bitstream.

Pour éviter ce problème il faut pouvoir lire la version du bitstream généré de manière à s’assurer qu’on travail bien avec la bonne.

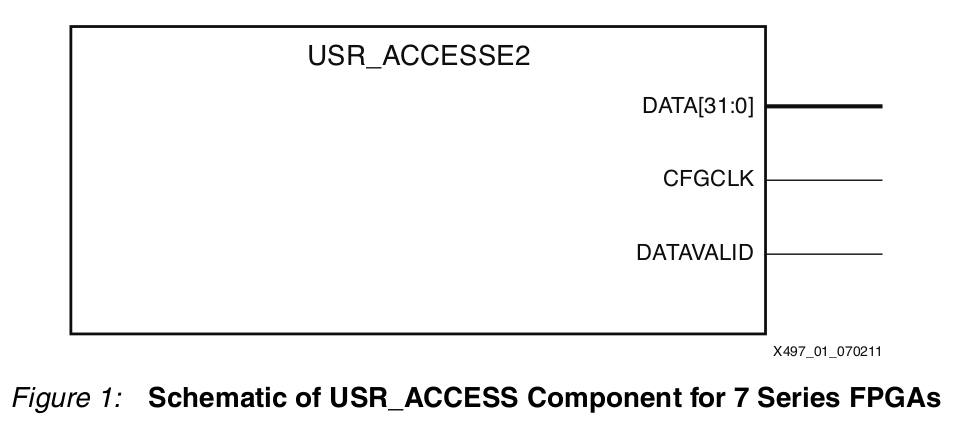

C’est exactement l’objet de la macro «usr_access» des FPGA de la série 7 de Xilinx.

Cette macro est appelée de la manière suivante en VHDL :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.all;

Entity usr_accesse2 is

port

(

CFGCLK : out std_logic;

DATA : out std_logic_vector(31 downto 0);

DATAVALID : out std_logic

);

end entity;

Architecture usr_accesse2_1 of usr_accesse2 is

begin

CFGCLK <= '1';

DATA <= x"00000E0F";

DATAVALID <= '1';

end architecture usr_accesse2_1;

Et la valeurs de la sortie «DATA» est ré-inscriptible jusqu’à la génération du bitstream avec l’option -g USR_ACCESS.

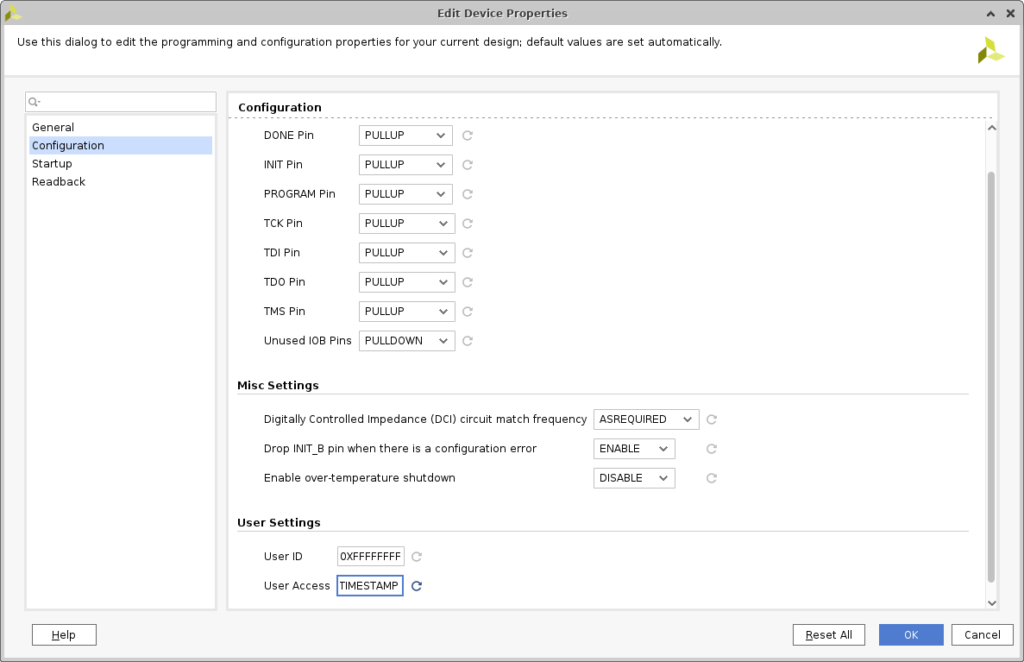

Pour y mettre la date et l’heure on utilisera l’option timestamp dans le menu tools->edit device property.

Cette action à pour effet d’ajouter la commande suivante dans le xdc :

set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design]Mais elle ne met pas la date chez moi pour le moment 🙁