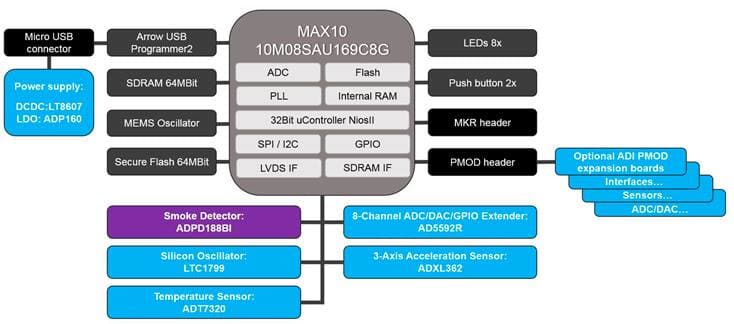

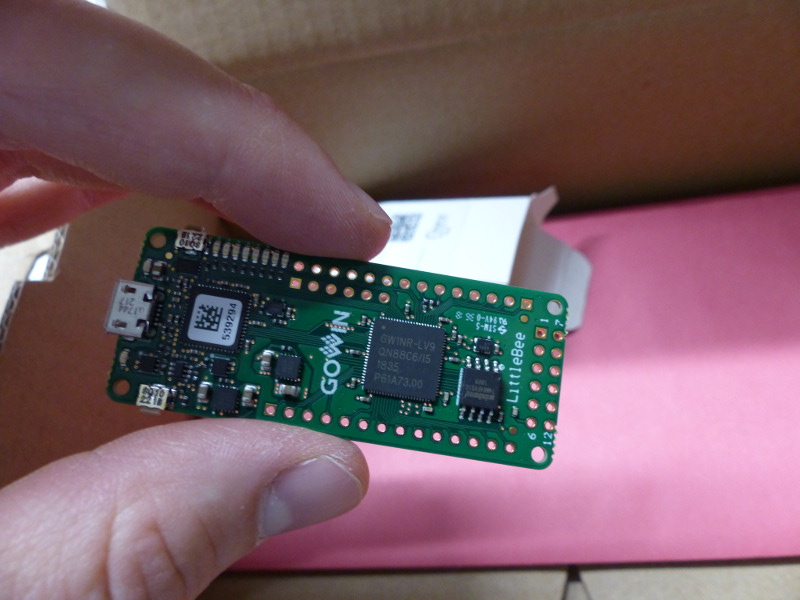

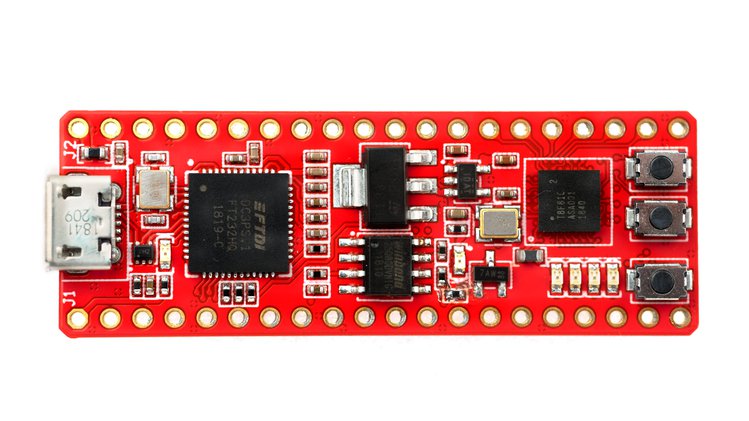

J’en avait déjà parlé dans les colonnes de ce blog. Une nouvelle société produit un FPGA nommé Trion T8. Ce FPGA est la base d’une petite carte de développement proposée par les HongKongais de XIPS Technology sur le site crowdsupply.

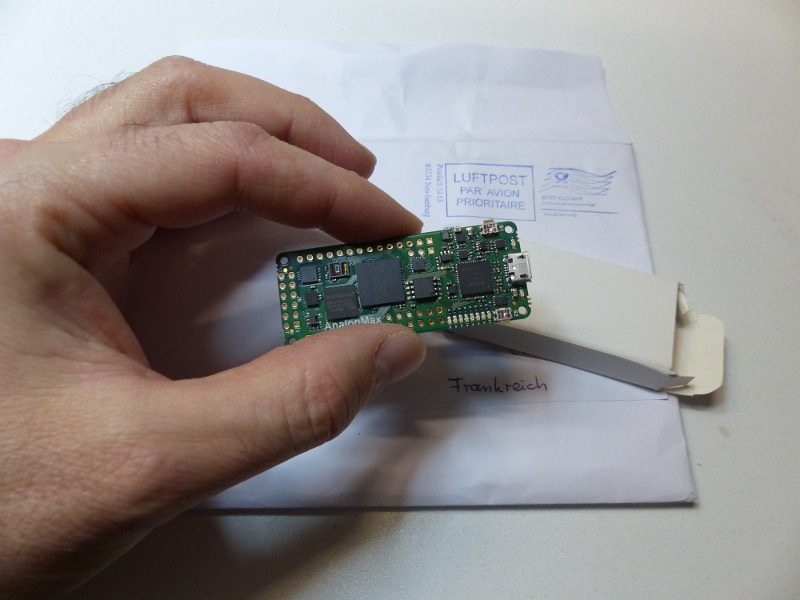

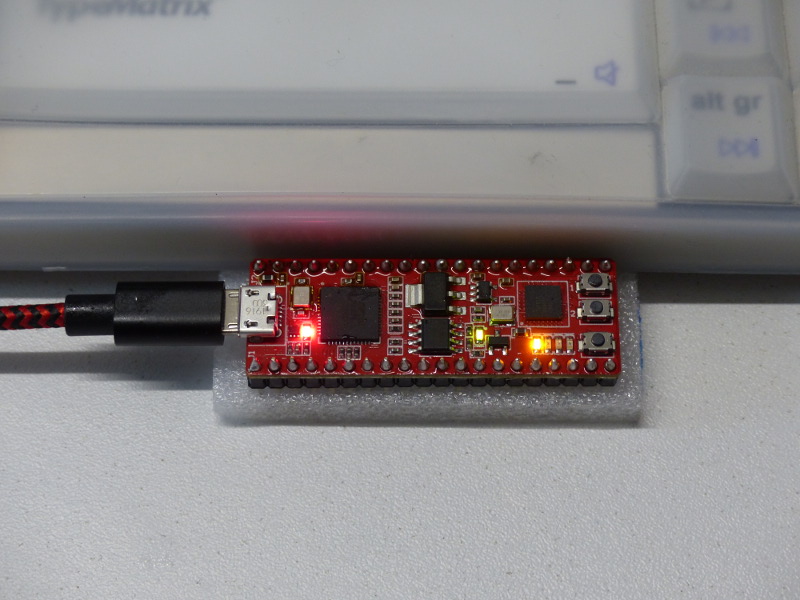

Évidemment je n’ai pas résisté à participer à la campagne. Quelques manifestations à HongKong et quelques déboire avec Fedex puis Mondial Relais, voici enfin le kit tant attendu arrivé chez moi.

Le kit est arrivé dans un énorme carton, mais c’est presque habituel dans ce genre de cas. J’avais pris sans les headers soudés mais ils sont tout de même fournis. J’ai juste eu à les souder moi même.

Au branchement une led rouge qui semble être celle de l’alimentation s’allume. Les 4 LED oranges se mettent elles à compter en binaire.

Dans les messages noyau nous avons la traditionnelle interface ttyUSB0 du FTDI :

$ dmesg

[97997.987953] usb 3-1: USB disconnect, device number 11

[97997.988359] ftdi_sio ttyUSB0: FTDI USB Serial Device converter now disconnected from ttyUSB0

[97997.988397] ftdi_sio 3-1:1.0: device disconnected

[98000.296737] usb 3-1: new high-speed USB device number 12 using xhci_hcd

[98000.445226] usb 3-1: New USB device found, idVendor=0403, idProduct=6014, bcdDevice= 9.00

[98000.445231] usb 3-1: New USB device strings: Mfr=1, Product=2, SerialNumber=0

[98000.445233] usb 3-1: Product: Single RS232-HS

[98000.445235] usb 3-1: Manufacturer: FTDI

[98000.446052] ftdi_sio 3-1:1.0: FTDI USB Serial Device converter detected

[98000.446118] usb 3-1: Detected FT232H

[98000.446278] usb 3-1: FTDI USB Serial Device converter now attached to ttyUSB0

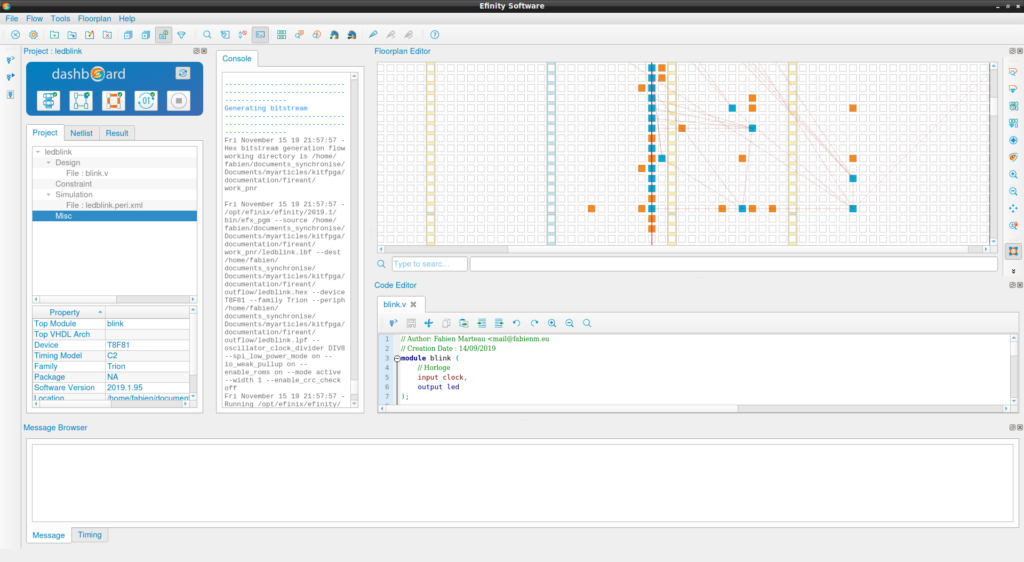

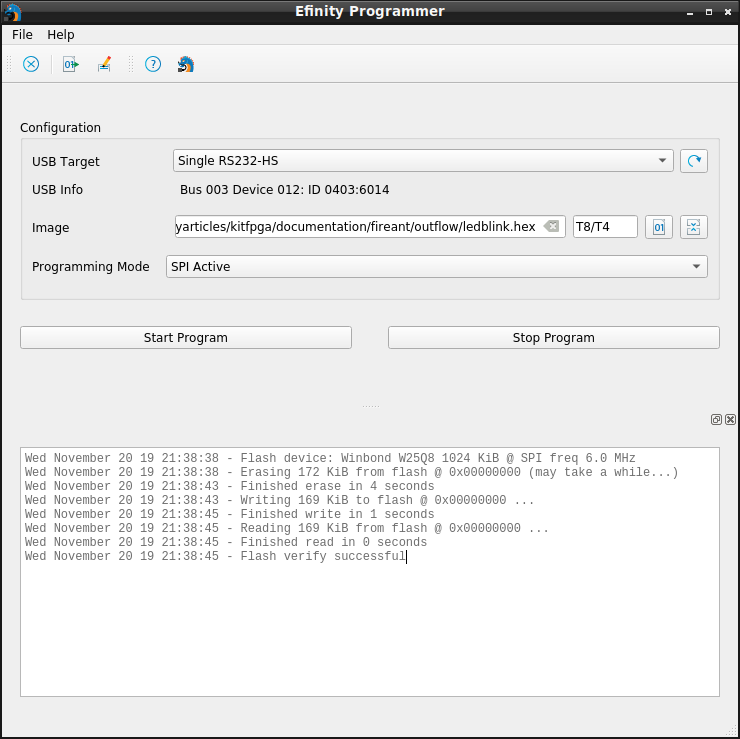

J’avais déjà reçu la license de la part de Efinix et Xips technology, du coup mon blinking led design était près à télécharger. Le bitstream est au format *.hex et se flash super facilement avec le Efinity programmer (tools -> programmer).

Par contre ma led ne clignote pas, je pense avoir encore quelques soucis avec les configs d’I/O et de PLL pour l’instant. Je doit encore me former à l’Efinity Interface Designer de Efinix qui est assez déroutant par rapport aux autres IDE.

[edit 28/01/2022]

Il est possible de charger le bitstream avec openFPGALoader sans problème de nos jours :

$ openFPGALoader -b fireant counter/outflow/counter.hex

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file DONE

Detail:

Jedec ID : ef

memory type : 40

memory capacity : 14

00

Detail:

Jedec ID : ef

memory type : 40

memory capacity : 14

flash chip unknown: use basic protection detection

Erasing: [==================================================] 100.00%

Done

Writing: [==================================================] 100.00%

Done

Wait for CDONE DONE

[ToBeEdited]