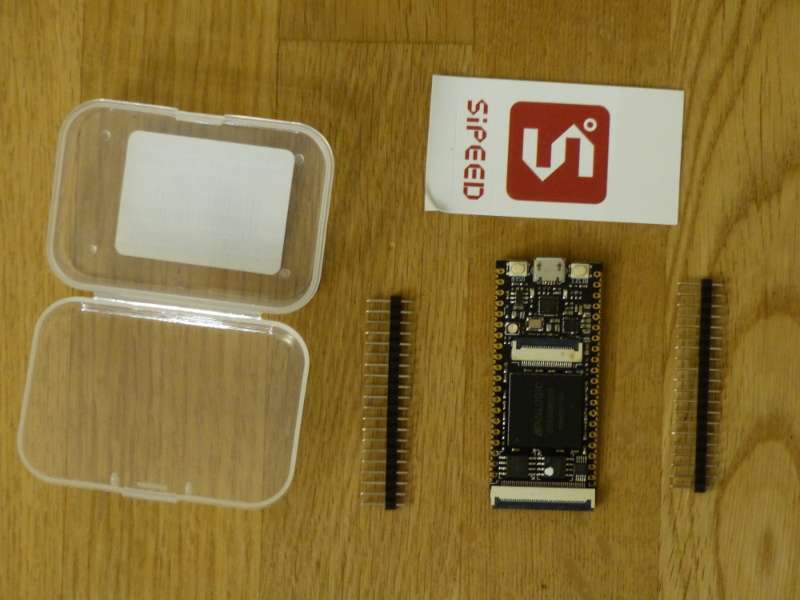

La société chinoise SiPeed propose un kit de développement permettant d’évaluer le FPGA chinois EG4S20BG256 produit par Anlogic. Le kit peut être commandé pour une vingtaine de dollars sur le site de vente en ligne Seeed spécialisé dans les kits de développement en électronique «grand public».

Au branchement du kit Debian/Linux détecte un convertisseur USB-JTAG de chez Anlogic:

$ sudo dmesg -c

[30017.300586] usb 3-2: new full-speed USB device number 5 using xhci_hcd

[30017.441796] usb 3-2: New USB device found, idVendor=0547, idProduct=1002

[30017.441801] usb 3-2: New USB device strings: Mfr=1, Product=2, SerialNumber=0

[30017.441804] usb 3-2: Product: USB-JTAG-Cable

[30017.441807] usb 3-2: Manufacturer: Anlogic

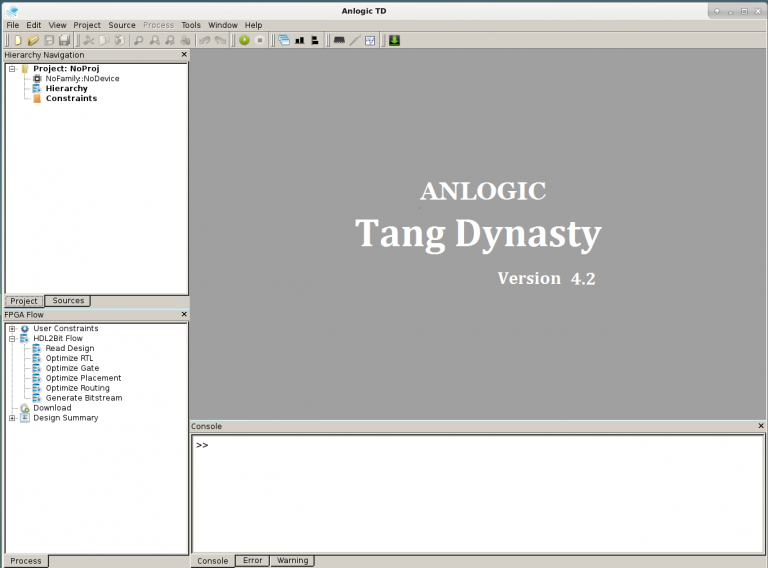

L’environnement de développement est disponible en téléchargement (~100Mo) sous forme d’une archive rar ici. Le fichier se décompresse avec la commande unrar:

$ unrar x ../TD_RELEASE_SEPTEMBER2018_RHEL.rar

Il faut ensuite mettre en exécutable le répertoire bin:

$ chmod +x bin/*

Et on peut ensuite lancer l’IDE:

$ cd bin ; ./td -gui

La fenêtre suivante s’ouvre alors :

C’est l’environement de développement le plus simple à installer que j’ai pu voir depuis que je bricole des FPGA. Même si la procédure d’installation est quand même étrange (un obscure .rar à télécharger puis à décompresser).

Pour synthétiser un premier design on va avoir besoin d’un minimum de documentation sur la schématique de la carte ainsi que sur le pinout du FPGA. On trouvera les schémas du kit en format pdf ici.

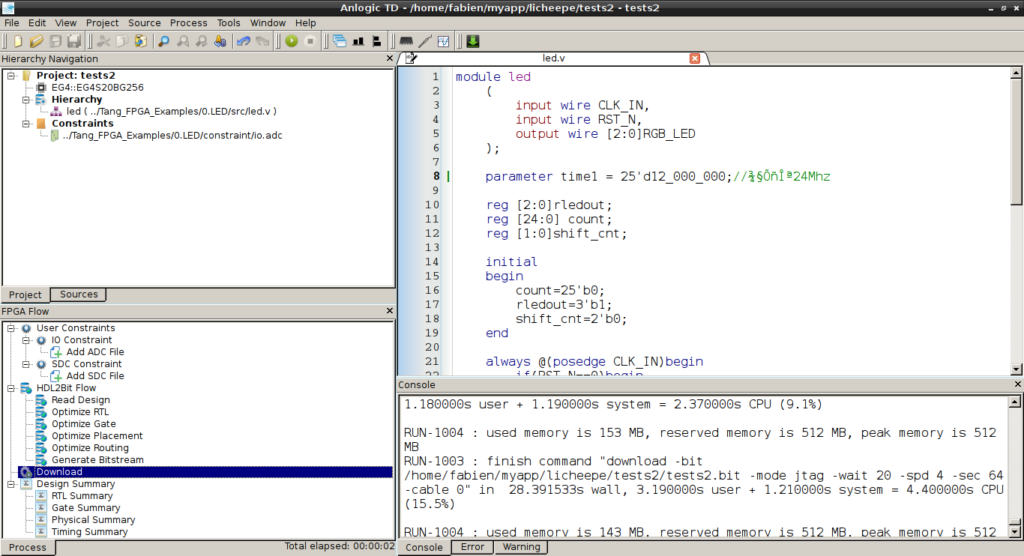

On trouve des exemples de code pour le kit sur github, notamment pour faire clignoter une led. La base du Hello World en électronique.

Pour tester la led qui clignote on crée un nouveau projet avec le fpga EG4S20BG256. On ajoute ensuite le source pour la led se trouvant dans le répertoire Tang_FPGA_Examples/0.LED/src/led.v

L’extension du fichiers de contrainte est en *.adc pour l’exemple de led le fichier se trouve dans le répertoire Tang_FPGA_Examples/0.LED/constraint/io.adc

Une fois les deux fichiers ci-dessus ajouté à notre projet on peut lancer la procédure complète pour générer le bitstream en double-cliquant sur l’icône «Generate Bitstream» dans l’encart «FPGA Flow» de l’ide.

La génération du bitstream est très rapide. Pour le télécharger ensuite dans le FPGA il faut bien sûr que le kit soit connecté à l’usb.

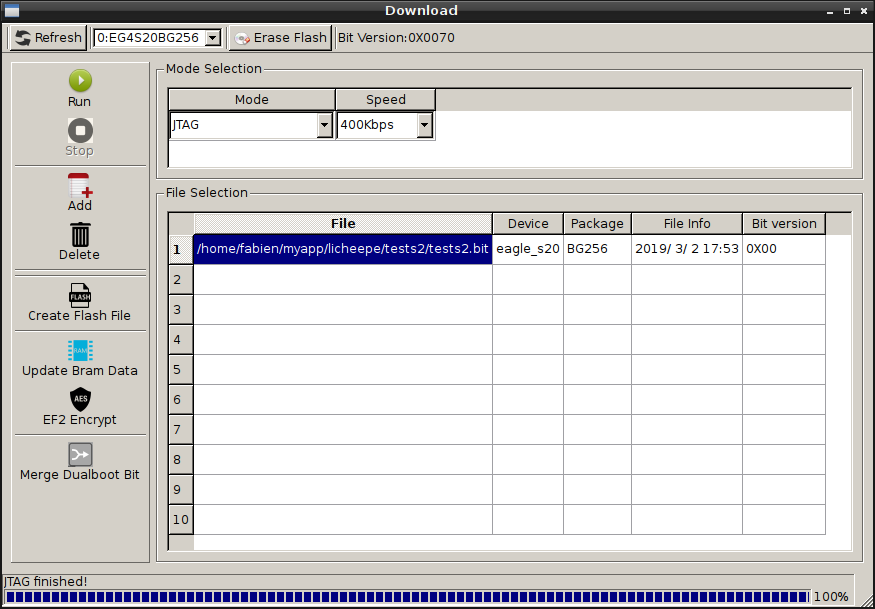

Le configurateur se lance en allant dans le menu Tools -> Download.

Chez moi j’ai du lancer l’ide en sudo pour éviter un plantage fatal, à ce moment. Le configurateur se présente comme ci-dessous :

Il faut ajouter le fichier bitstream au moyen du bouton de gauche «Add» puis cliquer sur la ligne du tableur pour «dégriser» le bouton «run», qui permet de télécharger le bitstream pour configurer le FPGA.

Pour conclure, je pensais beaucoup plus souffrir à mettre en route ce kit à la documentation majoritairement en chinois. Mais la note de blog de JAEB et le projet d’exemples sur github m’ont beaucoup aidé à faire clignoter cette led tricolore rapidement. À l’avenir il faudra regarder si ce FPGA est vraiment nouveau ou si ça n’est pas une copie d’un constructeur bien connu. On doit pouvoir vérifier ça avec le bitstream généré.

Au bout de quelques temps, la licence du logiciel expire. Il n’est plus possible de synthétiser avec. Un site chinois donne le truc pour que ça remarche. Pour éviter ce piratage, il semble être maintenant possible d’utiliser Yosys pour la partie synthèse !

La commande pour décompresser avec unrar est ‘unrar x’.

cf. la page man: https://linux.die.net/man/1/unrar

Corrigé.

Merci 😉

merci pour cet article !